# LA-UR-25-30842

# Approved for public release; distribution is unlimited.

Title: Al Assisted PCB Design to Increase Productivity and Efficiency

Author(s): Love, Jeffrey

Mu, Carrie

Intended for: Web

**Issued:** 2025-11-14 (rev.1)

Los Alamos National Laboratory, an affirmative action/equal opportunity employer, is operated by Triad National Security, LLC for the National Nuclear Security Administration of U.S. Department of Energy under contract 89233218CNA000001. By approving this article, the publisher recognizes that the U.S. Government retains nonexclusive, royalty-free license to publish or reproduce the published form of this contribution, or to allow others to do so, for U.S. Government purposes. Los Alamos National Laboratory requests that the publisher dientify this article as work performed under the auspices of the U.S. Department of Energy. Los Alamos National Laboratory strongly supports academic freedom and a researcher's right to publish; as an institution, however, the Laboratory does not endorse the viewpoint of a publication or guarantee its technical correctness.

#### AI Assisted PCB Design to Increase Productivity and Efficiency

The mission of ISR-4 (Space Electronics and Signal Processing) is to develop specialized sensors and systems designed for operation in demanding environments, including high radiation and space. As an integral part of Los Alamos National Laboratory (LANL), a federally funded research and development center, we contribute to advancing innovative technologies that meet critical national needs.

We conducted an evaluation of the Circuit Mind (CM) platform to determine whether to integrate their Al/Algorithm platform into our PCB production flow. Circuit Mind allows PCB designers to go from block diagrams to full schematics and bill of materials (BoM), using algorithms to determine requirements for cost, size, power, availability, etc. It automates tasks associated with schematic capture: selecting parts, verifying constraints (power, derating, supplier availability), generating verification reports (FMEA, etc.), and exporting schematic to ECAD tools. We performed two guided case studies to determine whether the platform would work in our PCB production flow.

For the evaluation we decided to place some limitations and constraints on the case study PCB block diagrams:

- We only used parts that were already available in the Circuit Mind database. Circuit

Mind engineers are routinely updating the database with new parts, based on their

customers' needs. For this evaluation we did not submit any requests for new parts to

be added to the database. Parts in the block diagram that are not available in the

database will be replaced with virtual blocks in the schematic.

- The two block diagrams we used for the case study were based on PCBs that had already been designed and manufactured. This allowed us to start the evaluation with schematics created by engineers that we could compare against the Circuit Mind output.

- We used Circuit Minds schematic symbols for the output schematic files. The platform

offers the ability to use our organization's schematic symbols, but setting up our Altium

tools to use their plugin would have delayed the start of the evaluation.

We chose two PCB designs for the evaluation; a medium difficulty design to help us learn how to use the platform with parts available in the database, and a high difficulty design using parts not in the database to see how the platform handles virtual blocks and demonstrate the capabilities of the Circuit Mind ACE tool.

The following process was used to evaluate each design:

Given: block diagram and specifications

- 1. Setup: Create block diagram in Circuit Mind platform

- 2. Solve: Circuit Mind generates PCB schematic, bill of materials and reports

- 3. Manual Post Automation Tasks: Task to be performed by engineer in ECAD tool (Altium)

- 4. Time Benchmarking:

Total Design Time = Setup Time + Solve Time + Manual Post Automation Time

- 5. Design Review

- 6. Design Exploration and Optimization

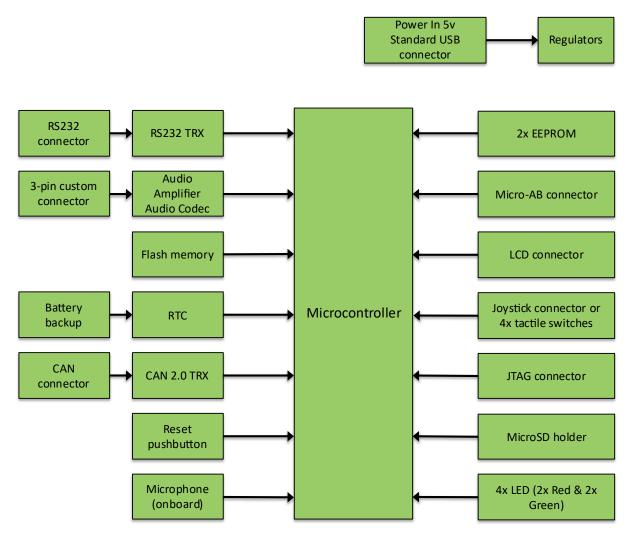

Each block diagram contains the IC component blocks in the design; only green components are fully supported by the platform. The medium difficulty design block diagrams are below.

Figure 1:Medium Difficulty Design Block Diagram

The requirements for the medium difficulty blocks are as follows.

| Component/Block                     | Requirement                                                                                                                                                                          |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Microcontroller                     | 1. Manufacturer: STMicroelectronics                                                                                                                                                  |  |  |

| Power Supply                        | Power Source: 5V Nominal     Power from a USB-C connector     Regulated supply for onboard components                                                                                |  |  |

| RS232                               | 1. RS-232 transceiver<br>2. 3 pin RS232 connector (RS232 Drivers, GND)                                                                                                               |  |  |

| CAN                                 | 1. CAN 2.0 transceiver 2. 3 pin CAN connector (CAN Bus Line, GND)                                                                                                                    |  |  |

| LCD                                 | 1. SPI LCD (Power Sink (Voltage: 3.3V), GND, SCK, MOSI, CS, RESET [Digital-In to connector], RS [Digital-In to connector])                                                           |  |  |

| JTAG connector                      | JTAG connector for debugging (JTAG Controller, Power [Power Sink, Voltage: 3.3V], GND)                                                                                               |  |  |

| Microphone                          | Analog microphone     Analog Out to microcontroller                                                                                                                                  |  |  |

| Speaker connector (Audio Output)    | 1. Audio Amplifier merged with Audio Codec IC 2. Output connector for speaker (Analog Pair from Audio Amplifier)                                                                     |  |  |

| LEDs, Joystick and Tactile Switches | 1. 2x LEDs (Emitting Color: Red) 2. 2x LEDs (Emitting Color: Green) 3. 4x Tactile switches (Joystick interface) 4. 1x Tactile switch (Digital In on microcontroller, RESET function) |  |  |

| EEPROM                              | 1. 2x units<br>2. Memory size > 64kbit                                                                                                                                               |  |  |

| FLASH memory                        | 1. Memory size > 512Mbit                                                                                                                                                             |  |  |

| Micro SD Holder                     | 1. Connector - Standard, Micro SD Card slot                                                                                                                                          |  |  |

| USB Micro AB connector              | 1. USB 2.0 interface                                                                                                                                                                 |  |  |

| Real Time Clock                     | <ol> <li>RTC</li> <li>Battery Holder (Power Source, Voltage: 3V, Battery Type<br/>CR2032)</li> <li>Crystal for time base</li> </ol>                                                  |  |  |

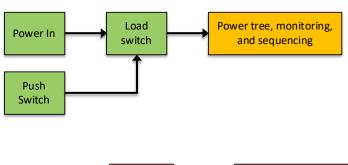

For the high difficulty design, yellow blocks are partially supported and red blocks are not supported.

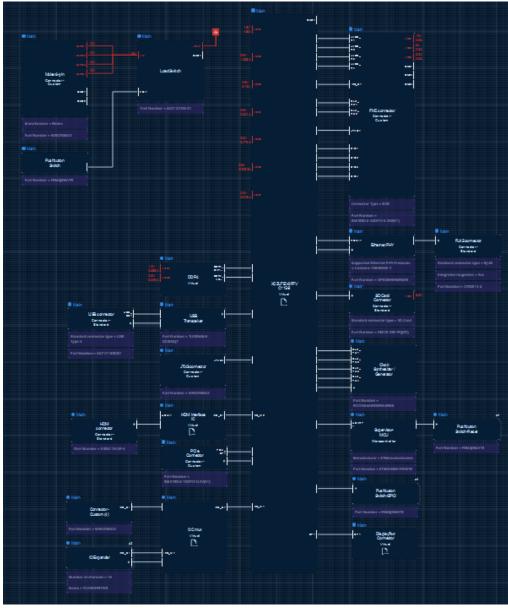

Figure 2: High Difficulty Design Block Diagram

| Component/Block         | Requirement                               |  |  |

|-------------------------|-------------------------------------------|--|--|

|                         | 1. Connector - Custom                     |  |  |

| Power input             | 2. Power Source: 12V and ground           |  |  |

|                         | 3. Manufacturer: Molex                    |  |  |

|                         | 1. Sink connected to input connector      |  |  |

| Load Switch             | 2. Digital-In interface                   |  |  |

|                         | 3. Default Power Source on output voltage |  |  |

| Pushbutton Switch (Load | 1. Connected to load switch Digital In    |  |  |

| switch)                 | 1. Connected to load switch Digital In    |  |  |

|                                                                                     | 1. Switching regulator                                     |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| 5V Regulator                                                                        | 2. Output voltage: 5V                                      |  |

|                                                                                     | 3. Input connected to Load switch output                   |  |

|                                                                                     | 1. Switching regulator                                     |  |

| 1.8V Regulator                                                                      | 2. Output voltage: 1.8V                                    |  |

| 1.6V Regulator                                                                      | 3. Input connected to 5V regulator output                  |  |

|                                                                                     | 4. Output to FPGA VCCIO                                    |  |

|                                                                                     | 1. Switching regulator                                     |  |

| 0.9V Regulator 1                                                                    | 2. Output voltage: 0.9V                                    |  |

| 0.34 Regulator 1                                                                    | 3. Input connected to 5V regulator output                  |  |

|                                                                                     | 4. Output to FPGA VCCINT                                   |  |

|                                                                                     | 1. Switching regulator                                     |  |

|                                                                                     | 2. Output voltage: 0.9V                                    |  |

| 0.9V Regulator 1                                                                    | 3. Input connected to 5V regulator output                  |  |

|                                                                                     | 4. Output to FPGA VCCINT_IO, VCCO, VCCAUX, VCCAUX_IO,      |  |

|                                                                                     | VCCAUX_BRAM                                                |  |

|                                                                                     | 1. Power Sink - VCCIO, Voltage: 1.8V, Current 1A           |  |

|                                                                                     | 2. Power Sink - VCCINT, Voltage: 0.9V, Current 1.263A      |  |

|                                                                                     | 3. Power Sink - VCCINT_IO, Voltage: 0.9V, Current 0.12A    |  |

| FPGA                                                                                | 4. Power Sink - VCCO, Voltage: 0.9V, Current 0.001A        |  |

| FFGA                                                                                | 5. Power Sink - VCCAUX, Voltage: 0.9V, Current 0.174A      |  |

|                                                                                     | 6. Power Sink - VCCAUX_IO, Voltage: 0.9V, Current 0.033A   |  |

|                                                                                     | 7. Power Sink - VCCAUX_BRAM, Voltage: 0.9V, Current 0.016A |  |

|                                                                                     | 8. BOM: Xilinx - XCZU7EV-2FFVC1156I                        |  |

|                                                                                     | 1. Connector - Custom                                      |  |

| JTAG Connector                                                                      | 2. JTAG Target and ground                                  |  |

|                                                                                     | 3. Connected to FPGA                                       |  |

| LIDAN Interference (C/V/interel)                                                    | 1. Virtual                                                 |  |

| HDMI Interface IC (Virtual) →  Is supported but CM does not  autrophy base any part | 2. HDMI Sink                                               |  |

|                                                                                     | 3. I2C Slave - I2C Addresses: 0x20                         |  |

| currently have any part                                                             | 4. BOM: Texas Instruments - TMDS181IRGZT                   |  |

| LIDAM Commands                                                                      | 1. Connector - Standard                                    |  |

| HDMI Connector                                                                      | 2. Connected to HDMI Interface IC                          |  |

| DCIa Connector                                                                      | 1. Connector - Custom                                      |  |

| PCIe Connector                                                                      | 2. PCIe Endpoint interface                                 |  |

|                                                                                     | 1                                                          |  |

|                                    | 1. Virtual Block                                                |  |  |

|------------------------------------|-----------------------------------------------------------------|--|--|

| I2C Mux                            | 2. I2C Master for IO Expander                                   |  |  |

| IZC Widx                           | 3. i2C slave to FPGA                                            |  |  |

|                                    | 4. BOM: Texas Instruments - PCA9544ARGYR                        |  |  |

|                                    | 1. 2x Instances                                                 |  |  |

| IO Expander                        | 2. Number of channels: 16                                       |  |  |

|                                    | IO going to regs enables, DDR etc. (Leaving the IO out for now) |  |  |

|                                    | 1. Connector - Custom                                           |  |  |

|                                    | 2. Power Sink, Voltage: 12V, Current 0.5A                       |  |  |

|                                    | 3. Power Sink, Voltage: 5V, Current 0.5A                        |  |  |

|                                    | 4. Power Sink, Voltage: 3.3V, Current 0.5A                      |  |  |

|                                    | 5. 8x LVDS receivers                                            |  |  |

| FPGA Mezzanine Card                | 6. I2C Slave                                                    |  |  |

| Connector                          | 7. 2x Clock Sink                                                |  |  |

|                                    | 8. JTAG Target                                                  |  |  |

|                                    | 9. 8x GPIO                                                      |  |  |

|                                    | 10. Connector Type: B2B                                         |  |  |

|                                    | 11. Connected to FPGA                                           |  |  |

|                                    | 12. Save connector for reuse                                    |  |  |

| USB Transceiver                    | 1. Connected to FPGA                                            |  |  |

|                                    | 1. Power Sink, 5V                                               |  |  |

| USB Connector                      | 2. USB SS (Super speed) interface connected to USB Transceiver  |  |  |

|                                    | 1. Virtual                                                      |  |  |

|                                    | 2. Power Sink - VDD, Voltage: 1.2V, Current: 0.363A             |  |  |

| DDR4                               | 3. Power Sink - VDD, Voltage: 2.5V, Current: 0.049A             |  |  |

|                                    | 4. DDR4 Interface (Data target and Address command control      |  |  |

|                                    | target)                                                         |  |  |

| Push Button Switch (FPGA)          | 1. 4x Instances                                                 |  |  |

|                                    | 2. Connected to FPGA                                            |  |  |

| Display Port Connector → <i>Is</i> | 1 Vietual                                                       |  |  |

| supported but CM does not          | 1. Virtual                                                      |  |  |

| currently have part                | 2. Digital in from FPGA (representative)                        |  |  |

| Missasantusllar                    | 1. USART Interface to FPGA                                      |  |  |

| Microcontroller                    | 2. Manufacturer: STMicroelectronics                             |  |  |

|                                    | IL                                                              |  |  |

| Push Button Switch | 1. 4x Instances                                                     |  |  |

|--------------------|---------------------------------------------------------------------|--|--|

| (Microcontroller)  | 2. Connected to Microcontroller                                     |  |  |

|                    | 1. Clock Synthesizer / Generator                                    |  |  |

| Clock              | 2. 4 Clock Source interface to FPGA ( <i>Original board has 6</i> ) |  |  |

|                    | NB: Clock frequency attribute not settable in ACE right now         |  |  |

|                    | 1. Connector - Standard                                             |  |  |

| SD Card            | 2. Power Sink, Voltage: 3.3V                                        |  |  |

|                    | 3. Standard connector type: SD Card                                 |  |  |

|                    | 1. Supported Ethernet PHY Protocols: Contains 1000BASE-T            |  |  |

| Ethernet PHY       | 2. RGMII connection to FPGA                                         |  |  |

|                    | 3. Use DP83869 (very similar to DP83867 used in design)             |  |  |

|                    | 1. Connector - Standard                                             |  |  |

| Ethernet Connector | 2. Standard connector type: RJ-45                                   |  |  |

|                    | 3. Integrated Magnetics: Yes                                        |  |  |

|                    | 4. Connected to Ethernet PHY                                        |  |  |

As part of the evaluation, each member of our evaluation team received a login for the CM platform and comprehensive training from CM engineers to gain hands-on experience. After the training we created the first case study design in the CM platform.

## **Medium Difficulty Design Results**

# Setup: Circuit Mind Functional Block Diagram – 35 minutes

# I. Circuit Mind Block Diagram

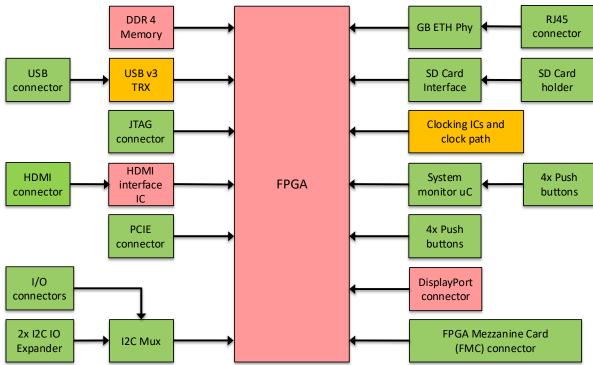

Low-level requirements, as outlined in the specification, can be captured in the CM block diagrams through the filter feature of each block component. These include manufacturer details, component-specific requirements (e.g. memory constraints, LED emission color), power and voltage parameters, communication protocols and interfaces, pin requirements, and interface functions.

Figure 3: Medium Difficulty Design Block Diagram in CM

## Solve: Automated Schematic, BoM, and Reports Generation – 8 minutes

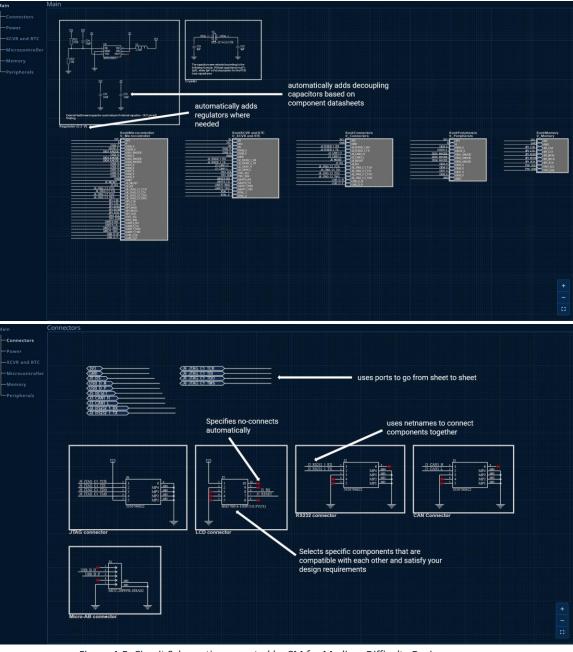

## I. Schematic Generation

Circuit Mind's schematic generation capability enables the design to be organized across multiple schematic pages for improved readability. It connects components through ports and net labels, while ensuring selected components are compatible and meet design requirements. The tool automatically incorporates decoupling capacitors according to component datasheets, specifies no-connects, and adds regulators where needed. Furthermore, schematics generated by CM can be exported to Altium, OrCAD, xPedition, or as a PCB project.

Figure 4-5: Circuit Schematic generated by CM for Medium Difficulty Design

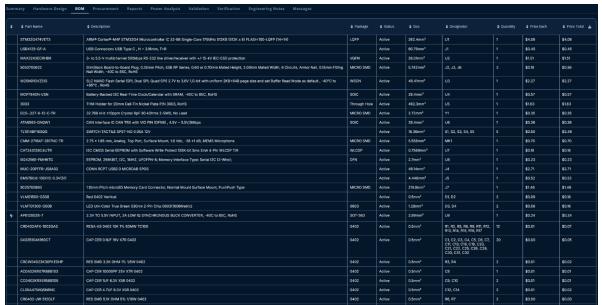

## II. Bill of Materials (BOM)

Itemized bill of materials based on components that CM selected in its generated schematic. The BOM can be exported as an Excel workbook or CSV.

Figure 6: Bill of Materials generated by CM for Medium Difficulty Design

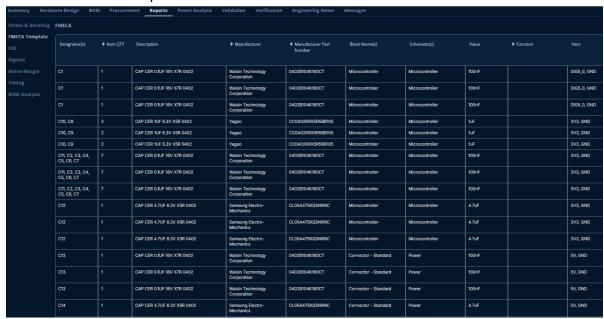

## III. Other Reports:

Additional reports generated by CM include stress, derating, and power analyses, an FMECA template, and an ICD report. Each can be exported as an Excel workbook or CSV for further use or completion.

Figure 7: Partially completed FMECA report generated by CM for Medium Difficulty Design

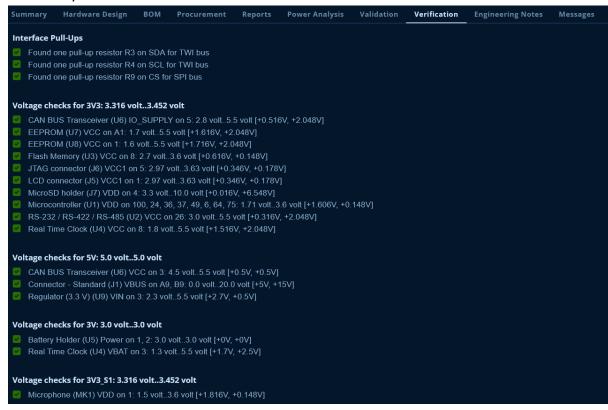

#### IV. Validation and Verification

CM validation confirms that the generated design satisfies all input specifications configured in the CM block diagram.

Figure 8: Validation Report generated by CM

CM verification performs checks on the design to ensure connections will function electrically.

Figure 9: Verification Report generated by CM

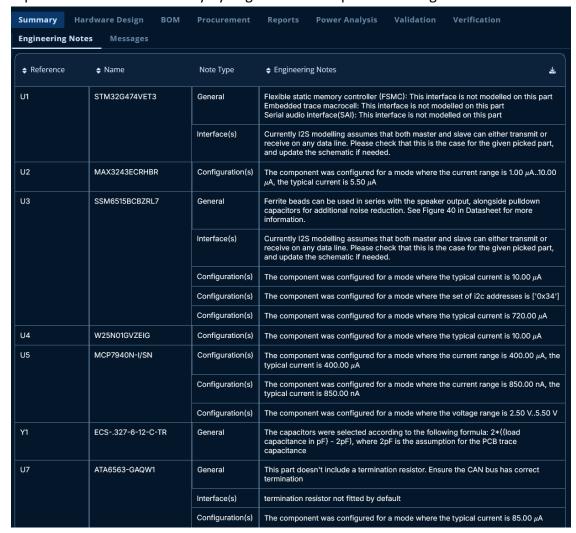

#### Manual Post Automation Tasks – 3.5 hours

#### I. Instructions outlined in engineering notes – Time expected: 1 hour

Circuit Mind keeps track of tasks it could not complete and lists them in the Engineering Notes. Some examples include fitting termination resistors or interface modelling. It also details certain assumptions/conditions that components must operate under. These reports should be read closely by engineers to complete the design.

Figure 10: Engineering notes that generated by CM, detailing any uncompleted tasks and assumptions

## II. Add unsupported components manually – Time expected: 2.5 hours

Unsupported components must be selected and connected to the rest of the schematic manually and in an ECAD tool. There are 3 components that need to be added manually for the medium difficulty design:

- 1) Add IrDA transceiver (1 hour)

- 2) Add potentiometer (30 min)

- 3) Audio Codec IC + Audio (1 hour)

#### **Benchmarking**

#### I. Time Benchmark: 4 hours 13 minutes

$Total\ Design\ Time = Setup\ Time + Solve\ Time + Manual\ Post\ Automation\ Time = 35\ minutes + 8\ minutes + 3.5\ hours$

= 4 hours 13 minutes

II. Manual Design Time Saved: 60 – 80 hours

III. Circuit Mind Completion Percentage: 90%

IV. Manual Engineer Completion Percentage: 10%

V. Time Saved with CM generated reports:

| Report            | Automation | Time Saved | Comment                                     |

|-------------------|------------|------------|---------------------------------------------|

| Automation        | 70%        | 1 month    | Each respin causes a 1 month delay. CM      |

| verification      |            |            | aims for first time right designs, removing |

|                   |            |            | 1 respin per project                        |

| FMEA Analysis     | 25%        | 2 weeks    | Failure modes and effects analysis (FMEA)   |

| Interface Control | 90%        | 7 hours    | Interface controls document for             |

| Document (ICD)    |            |            | programable interfaces                      |

| Procurement       | 90%        | 24 hours   |                                             |

| Power Analysis    | 70%        | 8 hours    | High level power analysis                   |

| Derating Analysis | 90%        | 16 hours   |                                             |

#### **Design Review Results**

After the design was completed by Circuit Mind, our evaluation team reviewed the generated design. We found that CM was able to complete a large majority of this design well but made a few minor errors and non-optimal choices. The manual corrections required are as follows:

- LED in-series resistor values need to be calculated manually and modified in ECAD tool.

- Micro AB connector 5V rail (VBUS) not connected.

## Design exploration and optimization: Iterative Design Results

## I. Can balance trade-offs and compare results

Users can optimize and iterate on their design in CM by balancing power, cost, and size tradeoffs and by adjusting constraints. These different designs can then be compared to identify the most optimal solution.

Figure 11: Comparison table for power optimized, cost optimized, size optimized, and balanced

# II. Edit with picked parts:

If a design component is suboptimal, users have the option to lock the satisfactory elements and regenerate the rest of the design.

Figure 12: Iterate medium difficulty design with edit with picked parts

## Pros and Cons of using CM for this design

The platform was able to complete the design in less than an hour, saving a lot of manual engineering time. As this was our first case study, we had to do some debugging to generate the design. The key was not to overly constrain the design.

## **High Difficulty Design Results**

## Setup: Circuit Mind Functional Block Diagram - 1 hour

I. Circuit Mind Block Diagram:

While the medium-difficulty design was chosen to demonstrate the Circuit Mind's capabilities, the high-difficulty design is intended to challenge and test its limits. Unsupported components, such as the FPGA and DDR4 memory, can be represented as virtual blocks. Engineers can define the interfaces of these virtual blocks to connect them with other blocks, but the actual part selection and pin wiring must still be done manually. While the tool can design power trees and sequencing, these features were not implemented in this design.

Figure 13: High Difficulty Design Block Diagram in CM

## Solve: Automated Schematic, BoM, and Reports Generation – 25 minutes

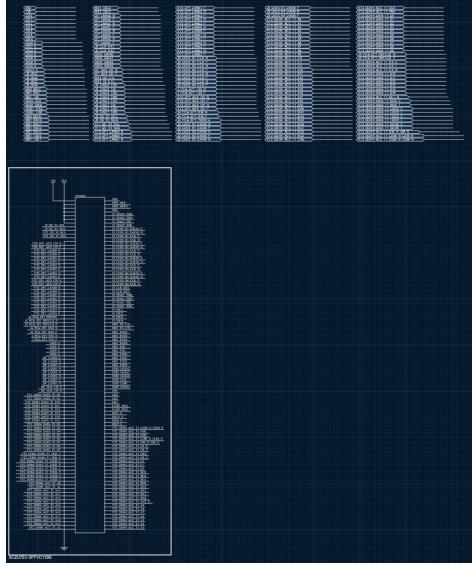

#### I. Schematic Generation:

The schematics include the same features as the medium difficulty design, with the main distinction being the addition of virtual blocks. These blocks only provide net names as placeholders and do not include reference designators or pin descriptors. As mentioned previously, the component selection and pin wiring must be configured manually.

Figure 14: Circuit Schematic generated by CM for High Difficulty Design

## II. Other CM Outputs:

In addition to the circuit schematic, CM generates a Bill of Materials, a derating analysis, an FMECA template, and an ICD report, consistent with the earlier design.

#### Manual Post Automation Tasks - ~80 hours

- I. Instructions outlined in engineering notes Time expected: 1 hour

- II. Add unsupported components manually Time expected: ~80 hours

The high-difficulty design requires five components to be added and connected manually:

- 1) Add FPGA (32 hours)

- 2) Add HDMI transceiver (6 hours)

- 3) Add Display port transceiver (6 hours)

- 4) Add DDR4 memory (32 hours)

- 5) Add i2C mux (4 hours)

## **Benchmarking**

I. Time Benchmark:

Total Design Time = Setup Time + Solve Time + Manual Post Automation Time

=

$$1 \text{ hour} + 25 \text{ minutes} + 80 \text{ hours}$$

=  $\sim 80 \text{ hours}$

- II. Manual Design Time Saved: 60 80 hours

- III. Circuit Mind Completion Percentage: 50%

- IV. Manual Engineer Completion Percentage: 50%

- V. Time saved by CM generated reports:

| Report            | Automation | Time Saved | Comment                                     |

|-------------------|------------|------------|---------------------------------------------|

| Automation        | 50%        | 160 hours  | Each respin causes a 1 month delay. CM      |

| verification      |            |            | aims for first time right designs, removing |

|                   |            |            | 1 respin per project                        |

| FMEA Analysis     | 20%        | 80 hours   | Failure modes and effects analysis (FMEA)   |

| Interface Control | 70%        | 10 hours   | Interface controls document for             |

| Document (ICD)    |            |            | programable interfaces                      |

| Procurement       | 90%        | 24 hours   |                                             |

| Power Analysis    | 70%        | 24 hours   | High level power analysis                   |

| Derating Analysis | 70%        | 16 hours   |                                             |

#### **Design Review Results**

The review identified the following manual corrections required for the generated high difficulty design:

- IO Expander signals need to be manually connected to connector and devices.

- Signal "DIG10\_0" has two 10K pullup resistors. Functional, but the second pullup is unnecessary.

- Exposed pad on load switch not connected to net.

- No magnetics on Ethernet connector.

## Pros and Cons of using CM for this design

Circuit Mind's ACE tool was able to complete the power design with just the requirements from the datasheet. Parts that were not in the database were replaced with Virtual Blocks, which increased the manual engineer completion ratio. Currently, the Circuit Mind platform does not support FPGAs, but the other parts could have been easily added to the database given time.

#### Conclusion

After conducting the evaluation, we have determined that the platform could work in our PCB production flow.